~半導体パッケージが一発でわかる図解ガイド~

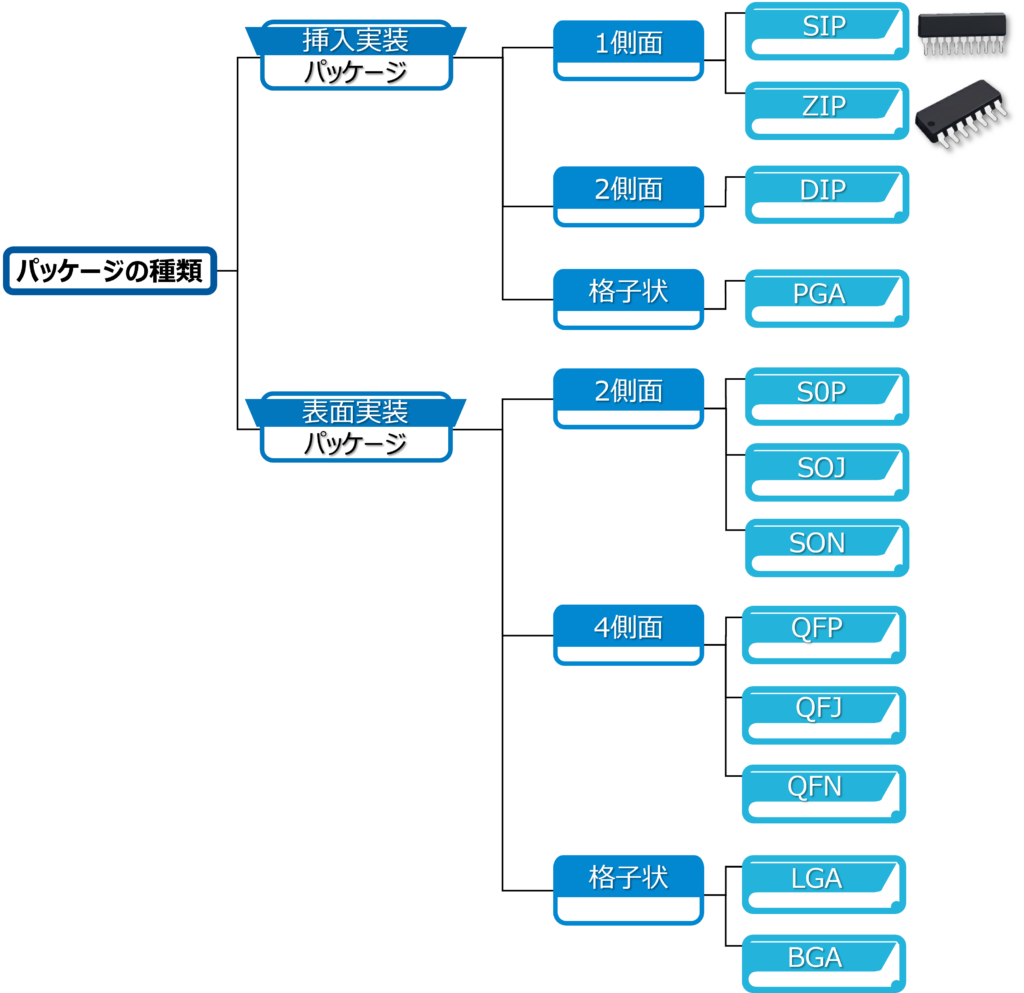

SIP・ZIP パッケージは半導体パッケージの一種です。パッケージは大きく 「挿入実装パッケージ」 と 「表面実装パッケージ」 に分類されます。

挿入実装パッケージは、基板にあけられたスルーホールにピンを差し込み、はんだ付けして固定する方式で、現在主流の表面実装と比べると古典的な技術です。しかし今日でも、

- 高い機械的強度が求められる用途

- 大電流を流す部品

- 教育用・実験用回路(ブレッドボード対応)

などで根強く利用されています。

挿入実装の歴史的パッケージとして、SIP・ZIP(シングル列)、DIP(双列)、PGA(格子状多数ピン)が存在します。それぞれをわかりやすく解説し、あわせて 検査・テスト工程で必要となる治具やコンタクトプローブ との関係を整理します。

SIP・ZIP シングル列パッケージが切り開いた“実装密度向上”の源流

シングル列パッケージの誕生とは

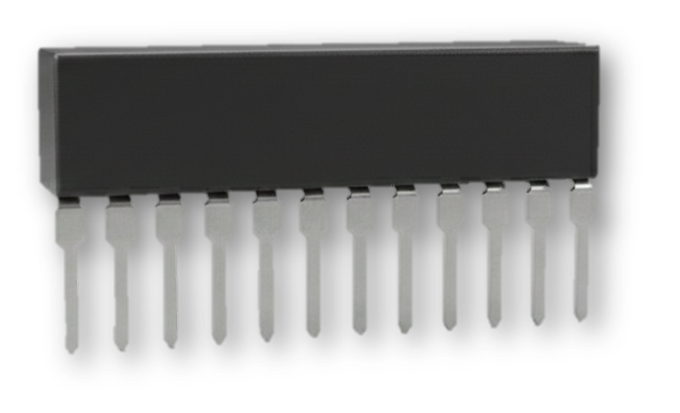

SIPとZIPは、どちらも “1列でピンを並べる” という非常にシンプルな思想から生まれた挿入実装パッケージです。表面実装が誕生する以前、限られた基板面積で回路規模を増やすために重要な役割を果たしました。

・SIP:ピンが一直線(ストレート) ・ZIP:ピンが千鳥配置(ジグザグ)

この2つは構造こそ似ていますが、「高密度化への工夫」という観点で明確な違いを持っています。

SIP(Single In-line Package)

SIP は、一方の側面にリードを縦一列で配列した細長いパッケージで、

- 実装密度が比較的高い

- 配置が直感的で試作しやすい

- 高さ方向に余裕がある設計に向く

といった特性を持ちます。

主な用途は

・抵抗アレイ ・センサ用 IC ・小規模アナログモジュール

などに広く使われていました。

今日では市場で見かける機会が減りましたが、縦長モジュールを必要とする産業用途では今も使用例があります。

ZIP(Zigzag In-line Package)

ZIP はSIP を改良した「高密度」パッケージで、“ピンをジグザグに折り曲げる” ことで、隣接ピッチを見かけ以上に広げつつ、パッケージ長を短縮できる工夫が施されています。

ZIP が登場した当時は「メモリ集積度の急増」に対応するキーパッケージでした。実装面積の削減で

- DRAM を中心としたメモリICで多く採用

- DIP よりもフットプリントが小さくできる

- ピン数増加要求に対応できた

現代では、BGA などの高密度パッケージに置き換わったため、アナログ ICや一部の電源モジュールなどの限られた用途にとどまります。

SIP・ZIP の技術的メリット・デメリット

| メリット | デメリット |

|---|---|

| 単純構造のため製造しやすい | 高さ方向をとるため薄型化には不向き |

| リードが強く、機械的強度が高い | 多ピン化に限界(SIP/ZIP は物理的制約が大きい) |

| 修理・交換が容易(教育用途に最適) | 表面実装と比較すると実装密度は低い |

検査・テスト工程で必要となる治具

SIP・ZIPの検査の特徴

細長い構造を持ち、かつピンが1列に並ぶため、リードの平行性・接触安定性が検査精度に大きく影響します。

使用される治具例

| ・SIP 専用 IC ソケット | ・垂直プローブを用いたコンタクトブロック |

| ・ZIP 深層挿入タイプソケット | ・手動治具(挿入ガイド付き) |

株式会社精研では、以下のような検査要件に対応可能です:

| 課題 | 精研のソリューション提案 *各ソリューションをクリックすると、該当するページに移動できます。 |

|---|---|

| 細長パッケージでの接触安定性確保 | コンタクトプローブ |

| 狭ピッチ ZIP での多点接触 | 細径・低荷重プローブ |

| 自動検査ラインへの組み込み | 治具一体型プローブブロック |

特に ZIP では「ピン角度が微妙にずれる」ケースがあるため、追従性の高いスプリングプローブが有効です。

SIP・ZIPは、今日の高密度パッケージに比べると古典的ですが、“高密度化の初期段階を支えた歴史的パッケージ”です。今日でも産業用途を中心に確かな需要があり、その検査ではリードのばらつきや狭ピッチ化による接触課題が発生しやすい形式です。もし検査工程で「接触が安定しない」「現行治具で歩留りが上がらない」などお困りの点がございましたら、ぜひお気軽にご相談ください。弊社のプローブおよび治具の提案により、最適な検査環境づくりをお手伝いさせていただきます。