~半導体パッケージ:SIP〜セラミックパッケージまで一挙紹介~

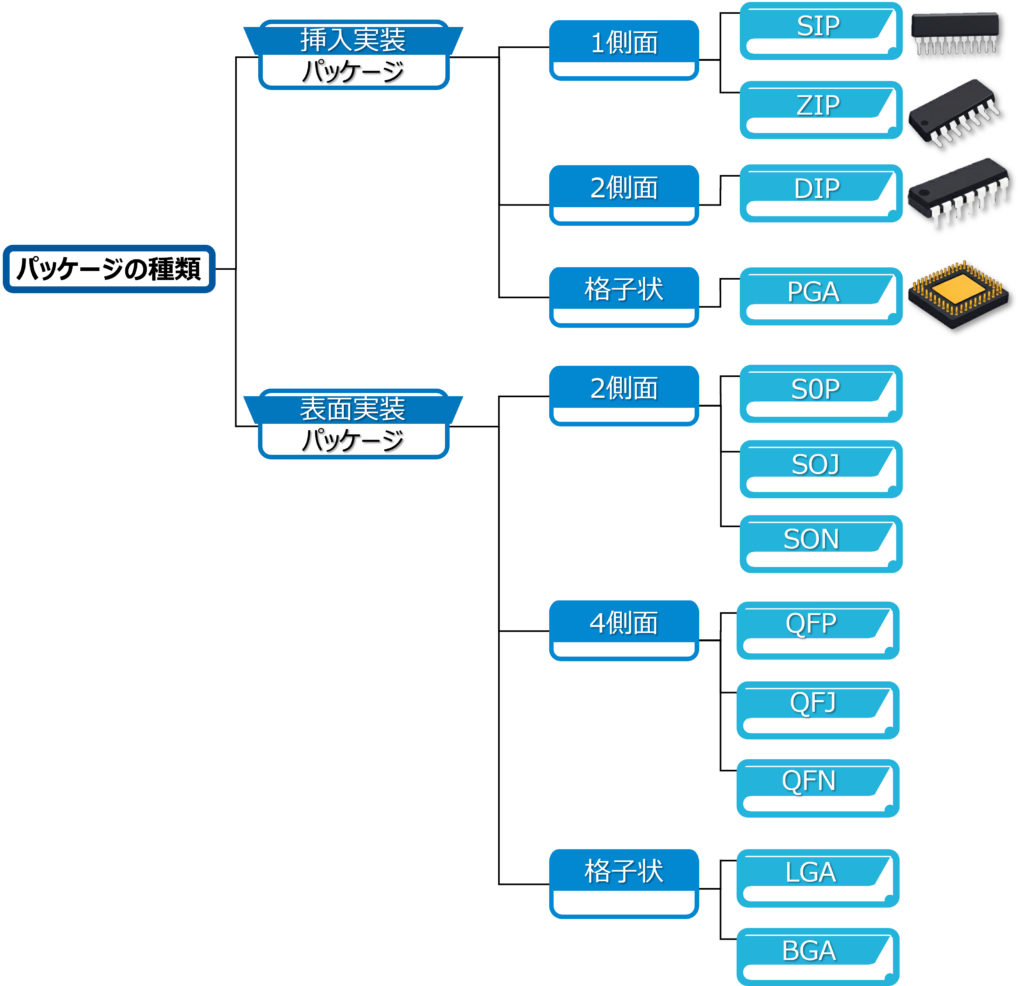

DIP・PGA は半導体パッケージの一種です。半導体パッケージは、挿入実装 と 表面実装 の2種類に大きく分けられます。挿入実装は、基板の穴にピンを差し込み、はんだ付けして固定する昔ながらの方式です。代表的な挿入実装パッケージとしては、 SIP/ZIP、DIP、PGA があり、本記事ではそれぞれの特徴と検査工程で関わる 治具・コンタクトプローブ について紹介します。

DIPやPGA― 多端子化の扉を開いた“挿入実装の主役たち”

挿入実装のメインストリームだった時代

DIPとPGAは、いずれも“ピン数を増やし、より高機能なICを実現するための歴史的パッケージ”です。

- DIP:両辺からピンが出る双列構造

- PGA:底面に格子状にピンを配置

特に 1980~1990 年代の電子機器では中心的な存在でした。大学の電子基礎実験でも非常に馴染みが深い形式です。

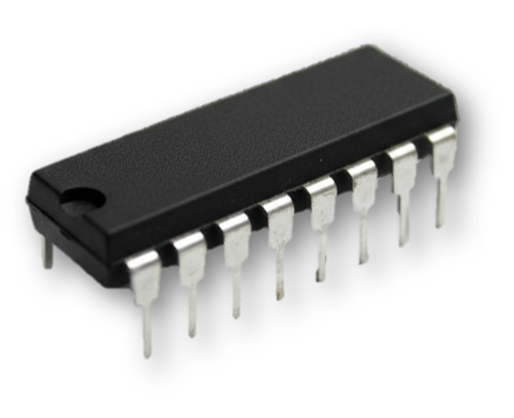

DIP(Dual In-line Package)

DIP は、パッケージ長辺の両側からピンが2列並ぶ最も一般的な挿入実装パッケージです。

多彩なバリエーションあります。

| ・PDIP(プラスチック) | ・WDIP(窓付き、EPROM 用) |

| ・CDIP(セラミック) | ・SDIP(薄型) |

DIPが長年にわたって使われ続けてきた理由は、手半田がしやすく機械的にも強度があり、さらにブレッドボードへそのまま挿せるといった「扱いやすさ」にあります。

主な用途

- ロジック IC(74シリーズなど)

- アナログ IC(オペアンプ)

- EPROM、マイコンの古い世代

など、教育機材から産業用途まで幅広い分野で利用されています。

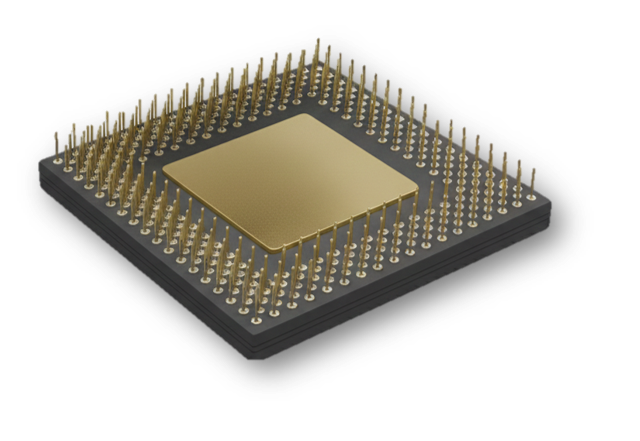

PGA(Pin Grid Array)

多ピン化を可能にした“格子状ピン”。PGA は、パッケージ底面に多数のピンを格子状に配置するパッケージで、DIP よりも圧倒的に多い端子数を実現できます。

PGA はかつての CPU パッケージとして広く使われ、Intel(Socket 7、Socket 370)やAMD(K6、Athlon など)で採用されていました。

特徴

- 多ピン化が容易

- 高い電気的性能を実現

- 誤挿入防止のため非対称配置(キーピン)を採用

現代では BGA(Ball Grid Array) に置き換えられましたが、サーバー用高信頼 IC でセラミック PGA が残存しています。

DIP・PGA の技術的メリット・デメリット

| メリット | デメリット |

|---|---|

| 修理・交換が容易 | 実装密度が低く、基板面積を多く使う |

| ソケット式での着脱検査が簡単 | 高速信号伝送には不向き |

| 多ピンに対応(特に PGA) | パッケージが大きく、携帯機器には向かない |

検査・テスト工程で必要となる治具

ピン数が多くなるほど、検査工程では「確実なピン接触」が重要になります。

DIP の検査で使われる治具

| ・ショート/オープン検査用プローブ治具 | ・高耐久ソケット付き評価基板 |

PGA の検査で必要な治具

PGA はピン数が膨大なため、

- 多点同時検査が可能なプローブブロック

- 接触抵抗を抑えるためのスプリングプローブ

- 自動挿抜に対応した治具一体型ソケット

が用いられます。

株式会社精研では、以下のような用途に対応できます:

| 検査課題 | 精研のソリューション提案 *各ソリューションをクリックすると、該当するページに移動できます。 |

|---|---|

| DIP の迅速な手挿し検査 | ソケット+スプリングプローブ治具 |

| 多ピン PGA の接触安定性確保 | ピンブロック/バイアスプローブ |

| 温度条件下での評価 | 高耐熱プローブ |

特に PGA の格子状ピンは「わずかな変形」で接触不良が生じやすいため、プローブ荷重のバランス設計が重要になります。

DIPやPGAは、今でも大事な役割を担っているパッケージです。ピン数が増えるほど「うまく接触しない」「治具が合わない」といった検査の悩みも出てきやすいです。そのような悩みがあれば、検査でちょっとした引っかかりや改善したいところがありましたら、お気軽にご相談ください。使いやすい治具やプローブの選定など、お客様のテスト環境に合わせて一緒にベストな方法を提案させていただきます。